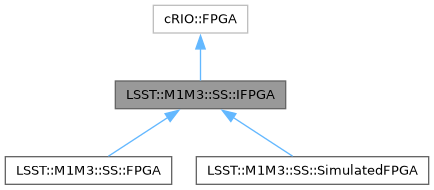

Abstract interface for FPGA. More...

#include <IFPGA.h>

Public Member Functions | |

| uint16_t | getTxCommand (uint8_t bus) override |

| uint16_t | getRxCommand (uint8_t bus) override |

| uint32_t | getIrq (uint8_t bus) override |

| SupportFPGAData * | getSupportFPGAData () |

| Call after pullTelemetry to retrieve telemetry data. | |

| HealthAndStatusFPGAData * | getHealthAndStatusFPGAData () |

| Call after pullHealthAndStatus to retrieve HealthAndStatus data. | |

| virtual void | waitForOuterLoopClock (uint32_t timeout)=0 |

| Wait for outer loop clock interrupt for synchronization between C++ and FPGA code. | |

| virtual void | ackOuterLoopClock ()=0 |

| Acknowledge (clear interrupt 0) outer loop clock. | |

| virtual void | waitForPPS (uint32_t timeout)=0 |

| Waits for Peer-to-Peer Synchronization interrupt (10). | |

| virtual void | ackPPS ()=0 |

| Acknowledge (clear) Peer-to-Peer Synchronization interrupt. | |

| virtual void | waitForModbusIRQs (uint32_t warning_timeout, uint32_t error_timeout)=0 |

| Wait for ModBus interrupts. | |

| virtual void | ackModbusIRQs ()=0 |

| Acknowledge ModBus interrupt reception. | |

| virtual void | pullTelemetry ()=0 |

| Retrieve telemetry data. | |

| virtual void | pullHealthAndStatus ()=0 |

| Retrieve Health&Status data. | |

| virtual void | writeTimestampFIFO (uint64_t timestamp)=0 |

| Write current timestamp value into timestampFIFO. | |

| virtual void | readU8ResponseFIFO (uint8_t *data, size_t length, uint32_t timeoutInMs)=0 |

| virtual void | writeHealthAndStatusFIFO (uint16_t request, uint16_t param=0)=0 |

| Requests HealthAndStatus data. | |

| virtual void | readHealthAndStatusFIFO (uint64_t *data, size_t length, uint32_t timeoutInMs=10)=0 |

| Copy HealthAndStatus data into supplied data buffer. | |

| virtual void | readRawAccelerometerFIFO (uint64_t *raw, size_t samples)=0 |

| Reads raw accelerometer FIFO. | |

| void | setPower (bool aux, bool network) |

| Sets all auxiliary and network buses power (A-D). | |

| void | setPower (const bool aux[4], const bool network[4]) |

| Sets aux and network power. | |

Static Public Member Functions | |

| static IFPGA & | get () |

Protected Attributes | |

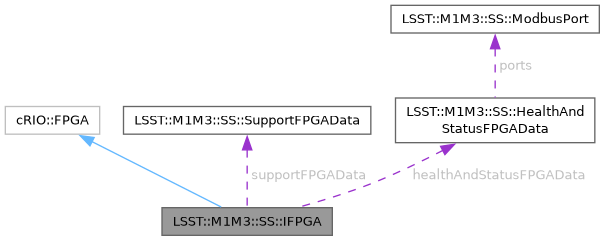

| SupportFPGAData | supportFPGAData |

| HealthAndStatusFPGAData | healthAndStatusFPGAData |

Detailed Description

Abstract interface for FPGA.

Both real FPGA and simulated class implements this. Singleton.

❗ Please see LSST::M1M3::SS::FPGA class for communication details.

Member Function Documentation

◆ ackModbusIRQs()

|

pure virtual |

Acknowledge ModBus interrupt reception.

Interrupt can be generated (raised on the FPGA side) again after being acknowledged.

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ ackOuterLoopClock()

|

pure virtual |

Acknowledge (clear interrupt 0) outer loop clock.

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ ackPPS()

|

pure virtual |

Acknowledge (clear) Peer-to-Peer Synchronization interrupt.

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ getHealthAndStatusFPGAData()

|

inline |

Call after pullHealthAndStatus to retrieve HealthAndStatus data.

- Returns

- HealthAndStatus data

◆ getSupportFPGAData()

|

inline |

Call after pullTelemetry to retrieve telemetry data.

- Returns

- telemetry data

◆ pullHealthAndStatus()

|

pure virtual |

Retrieve Health&Status data.

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ pullTelemetry()

|

pure virtual |

Retrieve telemetry data.

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ readHealthAndStatusFIFO()

|

pure virtual |

Copy HealthAndStatus data into supplied data buffer.

- Parameters

-

data memory data will be copied length buffer length. Must match FPGA defined memory size (64) timeoutInMs timeout in microseconds

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ readRawAccelerometerFIFO()

|

pure virtual |

Reads raw accelerometer FIFO.

Waits for new data if no data are available.

- Parameters

-

raw 8 raw accelerometer values. Data are stored as 24 bits fixed points (5 bits integer part) in uint64_t. So actually on 3 bytes out of 64 are used - that copies NI interface for accessing fixed points samples number of samples

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ readU8ResponseFIFO()

|

pure virtual |

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ setPower() [1/2]

| void IFPGA::setPower | ( | bool | aux, |

| bool | network ) |

Sets all auxiliary and network buses power (A-D).

- Parameters

-

aux auxiliary buses power (true = on) network network buses power (true = on)

◆ setPower() [2/2]

| void IFPGA::setPower | ( | const bool | aux[4], |

| const bool | network[4] ) |

Sets aux and network power.

- Parameters

-

aux[4] new auxiliar power, buses A-D network[4] new network power, buses A-D

◆ waitForModbusIRQs()

|

pure virtual |

Wait for ModBus interrupts.

The interrupt is generated when ModBus command 0x7 is processed.

- Parameters

-

warning_timeout warning timeout for IRQ call in milliseconds error_timeout after that time (in millisecond) expires, and error will be thrown

- Exceptions

-

NiError on NI error std::runtime_error on timeout

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ waitForOuterLoopClock()

|

pure virtual |

Wait for outer loop clock interrupt for synchronization between C++ and FPGA code.

The interrupt (0) is raised every 20 ms inside FPGA code (OuterLoop/OuterLoopClock.vi).

- Parameters

-

timeout after that time (in millisecond) expires, and error will be thrown

- Exceptions

-

NiError on NI error

- See also

- writeTimestampFIFO

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ waitForPPS()

|

pure virtual |

Waits for Peer-to-Peer Synchronization interrupt (10).

The interrupt is raised in Timestamp/Timestamp.vi and signals FPGA is ready to read peer time offset from TimestampControlFIFO.

- Parameters

-

timeout call timeout in milliseconds. TimeStamp VI introduces 1 milliseconds delay between successive waits for interrupt, so this value shall be larger than 1000.

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ writeHealthAndStatusFIFO()

|

pure virtual |

Requests HealthAndStatus data.

Response can be read calling readHealthAndStatusFIFO method.

Request types are:

- 1 return single U64 value at address param

- 2 return full HealthAndStatus memory. Size is specified when creating HealthAndStatus memory.

- 3 clear health and status memory

- Parameters

-

request request type, see above param relevant only for request 1

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

◆ writeTimestampFIFO()

|

pure virtual |

Write current timestamp value into timestampFIFO.

Shall be called after PPS interrupt is received. See NI forum for details.

- Parameters

-

timestamp current system timestamp in nanoseconds

- Exceptions

-

NiError on NI error

Implemented in LSST::M1M3::SS::FPGA, and LSST::M1M3::SS::SimulatedFPGA.

The documentation for this class was generated from the following files:

- FPGA/IFPGA.h

- FPGA/IFPGA.cpp

Generated by